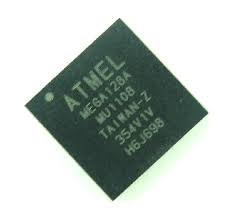

Read Chip ATmega128A EEPROM refers to a specialized technical process used to access binary and heximal data stored inside a secured ATmega128A microcontroller. This classic 8-bit AVR MCU integrates large on-chip flash, internal EEPROM, and SRAM, making it suitable for complex embedded program logic and long-term data retention. In many applications, critical firmware, configuration file data, and operational parameters are intentionally protected, locked, or even encrypted to prevent unauthorized duplication. When original source code or design documentation is lost, the ability to read and analyze EEPROM content becomes essential for system continuity.

From an engineering perspective, Read Chip ATmega128A EEPROM is not a simple attempt to open a device, but a disciplined form of reverse engineering. The process focuses on carefully extracting data from non-volatile memory, building a verified dump, and converting it into a structured archive that can be reviewed, validated, or reused. Protection fuses and security bits are designed to resist casual hack attempts, which means any effort to recover information must prioritize data integrity. The objective is not disruption, but controlled restore of valuable embedded knowledge without damaging the original chip.

The Atmel QTouch Library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR microcontrollers. The QTouch Library includes support for the QTouch and QMatrix acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch Library for the AVR Microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing API’s to retrieve the channel information and determine the touch sensor states.

The QTouch Library is FREE and downloadable from the Atmel website at the following location: www.atmel.com/qtouchlibrary. For implementation details and other information, refer to the

Atmel QTouch Library User Guide – also available for download from the Atmel website.

First Analog Comparator conversion may be delayed Interrupts may be lost when writing the timer registers in the asynchronous timer Stabilizing time needed when changing XDIV Register

Stabilizing time needed when changing OSCCAL Register

IDCODE masks data from TDI input

Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request

- First Analog Comparator conversion may be delayed

If the device is powered by a slow rising VCC, the first Analog Comparator conversion will take longer than expected on some devices.

Problem Fix/Workaround

When the device has been powered or reset, disable then enable theAnalog Comparator before the first conversion.

- Interrupts may be lost when writing the timer registers in the asynchronous timer

The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.

Problem Fix/Workaround

Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).

- Stabilizing time needed when changing XDIV Register

After increasing the source clock frequency more than 2% with settings in the XDIV register, the device may execute some of the subsequent instructions incorrectly.

Problem Fix / Workaround

The NOP instruction will always be executed correctly also right after a frequency change.

Thus, the next 8 instructions after the change should be NOP instructions. To ensure this, follow this procedure:

1.Clear the I bit in the SREG Register.

2.Set the new pre-scaling factor in XDIV register.

3.Execute 8 NOP instructions

4.Set the I bit in SREG

This will ensure that all subsequent instructions will execute correctly.

Assembly Code Example:

- Stabilizing time needed when changing OSCCAL Register

After increasing the source clock frequency more than 2% with settings in the OSCCAL register, the device may execute some of the subsequent instructions incorrectly.

Problem Fix / Workaround

The behavior follows errata number 3., and the same Fix / Workaround is applicable on this errata.

- IDCODE masks data from TDI input

The JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.

Problem Fix / Workaround

If ATmega128 is the only device in the scan chain, the problem is not visible.

Select the Device ID Register of the ATmega128 by issuing the IDCODE instruction or by entering the Test-Logic-Reset state of the TAP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYPASS instruction to the ATmega128 while reading the Device ID Registers of preceding devices of the boundary scan chain.

If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the ATmega128 must be the fist device in the chain.

- Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request.

Reading EEPROM by using the ST or STS command to set the EERE bit in the EECR register triggers an unexpected EEPROM interrupt request.

The ATmega128A has been widely deployed across industrial automation, power control units, medical instruments, security systems, and communication equipment. Its balanced performance and rich peripheral set make it ideal for products that require stability over many years. As equipment ages, manufacturers may face discontinued components, third-party ownership changes, or missing backups. In such cases, being able to read EEPROM and flash content from a protected microprocessor enables maintenance teams to replicate boards, troubleshoot failures, or migrate designs to newer platforms without starting from zero.

The difficulty lies in the protection itself. Secured ATmega128A devices employ multiple layers of safeguards that increase the risk of data loss if mishandled. That is why detailed techniques are never publicly disclosed. For clients, however, the meaning of Read Chip ATmega128A EEPROM is straightforward: it safeguards intellectual property, reduces redevelopment costs, and minimizes downtime. By transforming inaccessible firmware and data into a usable archive, this process delivers long-term value—supporting legacy systems, enabling compliant duplication, and preserving mission-critical embedded systems well beyond their original lifecycle.