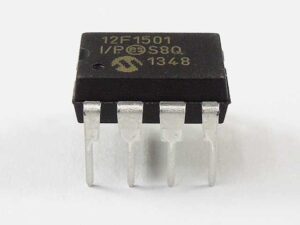

Readout Microchip PIC12F1501 Controller Heximal Data start from Asynchronous Reception Set-up:

1. Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 22.4 “EUSART Baud Rate Generator (BRG)”).

2. Clear the ANSEL bit for the RX pin (if applicable).

3. Enable the serial port by setting the SPEN bit for the purpose of Copy Microchip PIC16F1707 Processor Software. The SYNC bit must be clear for asynchronous operation.

4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

5. If 9-bit reception is desired, set the RX9 bit.

6. Enable reception by setting the CREN bit.

7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set as a result of Microchip MCU PIC16F1705 Embedded Firmware Extraction.

8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

9. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

9-bit Address Detection Mode Set-up can affect Readout Microchip PIC12F1501 Controller Heximal Data too:

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate

- Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation after Copy Microprocessor PIC18F8585 Flash Memory.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- Enable 9-bit reception by setting the RX9 bit.

- Enable address detection by setting the ADDEN bit.

- Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer to facilitate the process of Extract MCU PIC18F8525 Source Code. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device’s address.

- If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

If the device has been addressed in the process of Crack MCU Memory, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.