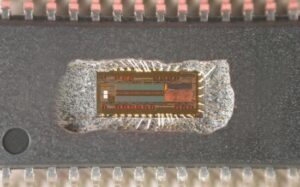

Copy Heximal from Protected Microcontroller PIC18F2685 is a process to unlock protected microprocessor pic18f2685 flash memory, this is called reverse engineering pic18f2685 mcu code;

Selecting a power managed mode requires two decisions: if the CPU is to be clocked or not and the selection of a clock source. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS1:SCS0 bits (OSCCON<1:0>) select the clock source to facilitate the process of Copy Heximal from Protected Microcontroller PIC18F2685. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

The SCS1:SCS0 bits allow the selection of one of three clock sources for power managed modes. They are:

- the primary clock, as defined by the FOSC3:FOSC0 configuration bits

- the secondary clock (the Timer1 oscillator)

- the internal oscillator block (for RC modes) when Extract IC ATTINY13 Code

Switching from one power managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used.

Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays in order to Read Microcontroller ATTINY12 Firmware.

These are discussed in Section 3.1.3 “Clock Transitions and Status Indicators” and subsequent sections. Entry to the Power Managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit. Depending on the current mode and the mode being switched to, a change to a power managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction before the Extract MCU ATTINY13V Heximal.

If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode. The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

- OSTS (OSCCON<3>)

- IOFS (OSCCON<2>)

- T1RUN (T1CON<6>)Three bits indicate the current clock source and its status. They are:

- In general, only one of these bits will be set while in a given power managed mode. When the OSTS bit is set, the primary clock is providing the device clock after Unlock microcontroller.