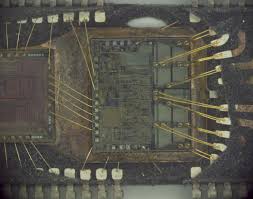

Altera CPLD EPM7256BTI144 Eeprom Data Extraction needs to attack the security fuse bit of cpld epm7256bti144 eeprom and then decrypt the jed file from cpld epm7256bti144 eeprom memory;

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions.

Large-amplitude, fast-ground- current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result when copying altera cpld epm7128buc169 eeprom firmware.

Numbers in brackets are for 2.5-V outputs. Numbers without brackets are for 3.3-V outputs.

MAX 7000A device timing can be analyzed with the Altera software, a variety of popular industry-standard EDA simulators and timing analyzers, or with the timing model shown in Figure 11.

MAX 7000A devices have predictable internal delays that enable the designer to determine the worst-case timing of any design. The software provides timing simulation, point-to-point delay prediction when restoring altera cpld epm7128elc84 eeprom content, and detailed timing analysis for device-wide performance evaluation.

The timing characteristics of any signal path can be derived from the timing model and parameters of a particular device. External timing parameters, which represent pin-to-pin timing delays, can be calculated as the sum of internal parameters. Figure 12 shows the timing relationship between internal and external delay parameters.